Elektronik & PCB

CT- und Laminographie-Prüfung für Elektronik – Lötfehler in BGAs und PCBs zuverlässig erkennen. BGA-Lotstellen, versteckte Brücken, Via-Fehler: Microvistas Laminographie-Technologie analysiert Leiterplatten und Elektronik-Baugruppen hochauflösend – ohne die Platine zu zerstören.

Diese Probleme kennen wir

BGA-Lotstellen sind von außen nicht prüfbar – Fehler bleiben bis zum Ausfall verborgen

Ball-Grid-Array-Komponenten haben ihre gesamten Lötverbindungen unter dem Bauteilgehäuse verborgen – eine visuelle Inspektion nach dem Löten ist vollständig ausgeschlossen. Cold Joints, Missing Solder und Bridging bleiben deshalb unentdeckt und führen erst unter thermomechanischer Beanspruchung im Feld zum Ausfall. In sicherheitskritischen Steuergeräten – etwa in Automotive-ECUs oder Avionik-Systemen – kann ein einziger fehlerhafter Lötkontakt schwerwiegende Folgen haben.

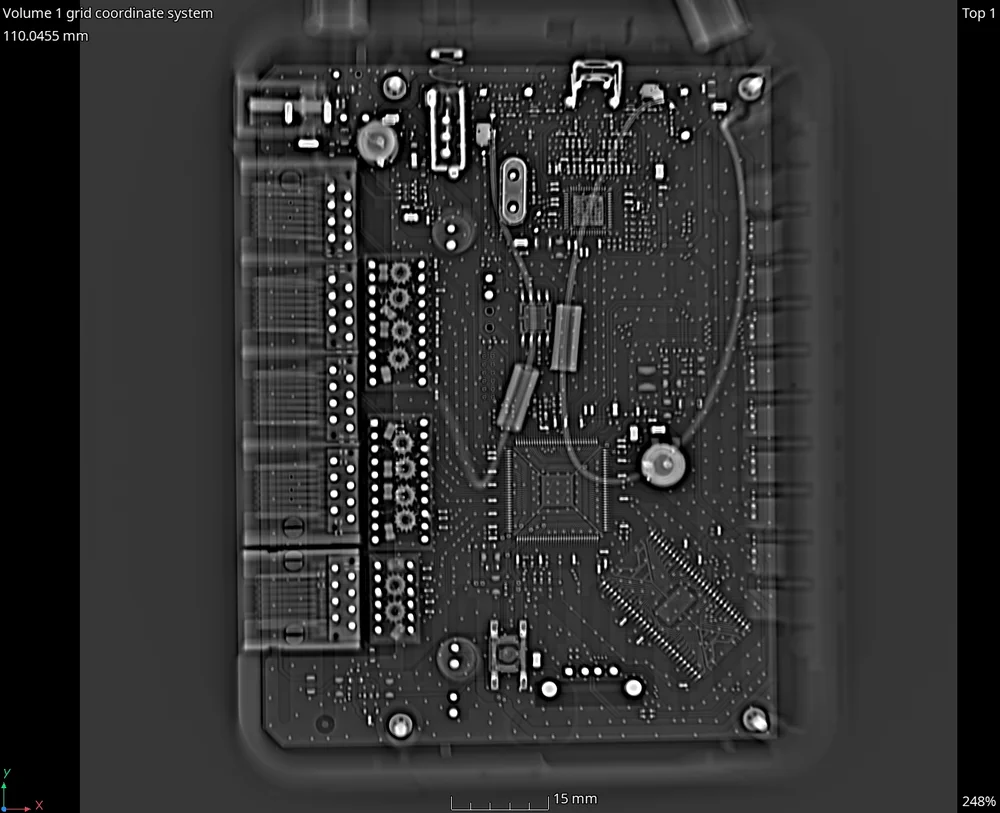

Klassische Röntgenprüfung überlagert Schichten und kann Bridging nicht eindeutig klassifizieren

2D-Röntgenprüfung projiziert alle Lagen einer Leiterplatte übereinander, wodurch Signale aus verschiedenen Schichten sich überlagern und Bridging zwischen benachbarten Pads nicht sicher von korrekten Verbindungen unterscheidbar ist. Bei modernen Hochdichte-PCBs mit mehreren Lagen und feinen Pitch-Abständen führt das zu hohen Falschpositivraten und gleichzeitig zu nicht erkannten echten Fehlern. Eine verlässliche Klassifikation ist ohne schichtgenaue 3D-Analyse nicht möglich.

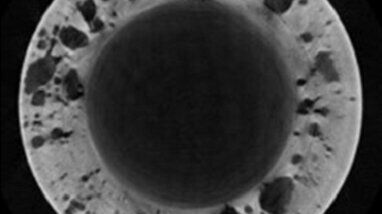

Void-Analyse in kritischen Lötstellen erfordert hochauflösende 3D-Daten

Gasblasen (Voids) in Lötstellen unter Leistungskomponenten wie IGBTs oder SiC-Modulen verschlechtern den Wärmeübergang erheblich und führen unter Dauerlast zu Überhitzung und vorzeitigem Ausfall. IPC-7095 definiert zulässige Void-Grenzwerte, deren Einhaltung nur durch vollständige 3D-Volumenanalyse der Lotstelle nachgewiesen werden kann. 2D-Röntgen unterschätzt das Void-Volumen systematisch, weil Überlagerungen die tatsächliche Größe verschleiern.

NTF-Rückläufer (No Trouble Found) kosten Zeit und Geld, weil die Fehlerursache unklar bleibt

Ein erheblicher Teil der Elektronik-Rückläufer aus dem Feld lässt sich beim Hersteller nicht reproduzieren – die Fehlerursache bleibt ungeklärt. Jeder NTF-Fall kostet mehrere Hundert Euro für Prüfaufwand, Logistik und Garantieabwicklung, ohne dass das eigentliche Problem gelöst wird. CT-gestützte Failure Analysis identifiziert verborgene Ursachen wie Mikrorisse, Delaminierungen oder intermetallische Phasen zuverlässig und bildet die Grundlage für nachhaltige Prozessverbesserungen.

CT-Lösungen für Elektronik & PCB

Laminographie (LayerScan)

Microvistas LayerScan-Technologie erzeugt hochauflösende Schichtbilder von flachen Leiterplatten, ohne dass eine vollständige 360°-Drehung der Platine erforderlich ist. Das ermöglicht die präzise Analyse einzelner PCB-Lagen unabhängig voneinander – Bridging, Void-Verteilung und Lotstellen-Geometrie werden schichtgenau ausgewertet. Im Vergleich zu konventioneller Röntgenprüfung werden signifikant mehr echte Fehler erkannt bei gleichzeitig deutlich geringerer Falschalarmrate.

BGA & QFN Inspektion

Microvista analysiert vollständig alle Lotstellen unter BGA-, QFN- und ähnlichen flächigen Komponenten in 3D auf Void-Gehalt, Cold Joints, Bridging und Missing Solder. Das Ergebnis ist eine schematische Darstellung aller Lotstellen mit Klassifikation nach IPC-7095 und einem sofort verwendbaren Prüfprotokoll. Fehlerquoten und typische Fehlerbilder werden statistisch ausgewertet, was gezielte Prozessverbesserungen im Reflow-Prozess ermöglicht.

Via-Analyse

Microvista prüft Durchkontaktierungen und Micro-Vias in Hochdichte-Leiterplatten auf Unterbrechungen, innere Hohlräume und unvollständige Füllung, die zu intermittierenden Ausfällen führen. Besonders bei HDI-Platinen mit gefüllten und überlagerten Vias ist CT die einzige Methode, die den tatsächlichen Füllgrad und die Verbindungsintegrität jeder einzelnen Via zuverlässig bewertet. Das Ergebnis bildet die Grundlage für Freigabeentscheidungen und Lieferantenqualifizierungen.

Failure Analysis Elektronik

Microvista führt vollständige CT-basierte Failure-Analysis-Untersuchungen von Elektronikbaugruppen durch und lokalisiert Fehlerursachen wie Mikrorisse, Delaminierungen, intermetallische Phasenbildung und Korrosion in der dritten Dimension. Das Schadensprotokoll enthält eine präzise Lokalisierung und Bewertung der Fehlerursache sowie Empfehlungen für Prozessverbesserungen. NTF-Fälle werden so in fundierte Erkenntnisse für die Qualitätssicherung umgewandelt.

Anwendungsfälle

BGA-Baugruppen in Automotive-Steuergeräten (ECU, BCM, TCM): CT analysiert alle Lotstellen nach IPC-7095, erkennt Void-Überschreitungen und Cold Joints, die im Feldeinsatz zu Steuergeräteausfällen führen würden.

Leistungselektronik – IGBT-Module und SiC-Inverter: 3D-Void-Analyse der Lötstellen auf Einhaltung thermischer Grenzwerte – entscheidend für Lebensdauer und Betriebssicherheit.

Consumer Electronics – Smartphone-Platinen: Laminographie prüft feinste BGA-Verbindungen bei miniaturisierten Baugruppen mit Pitch unter 0,4 mm auf Lötstellen-Integrität.

Luft- und Raumfahrt-Avionik: Sicherheitskritische Boardprüfung mit vollständiger CT-Dokumentation aller Lötstellen für NADCAP- und DO-254-Konformitätsnachweise.

Überzeugende Zahlen

So arbeiten wir

CT-Labor

Hochauflösende Prüfung im akkreditierten Labor für Einzelprüfungen und Erstmuster.

Mehr erfahren → Express verfügbarScanExpress

Mobiles CT direkt bei Ihnen vor Ort für Großbauteile und schnelle Serienprüfung.

Mehr erfahren →Cloud-Auswertung

Flexible Auswertung Ihrer CT-Daten mit unserer sicheren Cloud-Plattform.

Mehr erfahren →Passende Prüfaufgaben für Elektronik & PCB

Laminographie

Laminographie für flache Bauteile: Leiterplatten, Elektronikbaugruppen und Verbundwerkstoffe hochauflösend analysieren.

Prüfaufgabe öffnen →Montage- & Fügekontrolle

Montage & Fügekontrolle kinderleicht: Industrielle CT prüft das Verhalten einer montierten Baugruppe automatisch in verschiedenen Zuständen.

Prüfaufgabe öffnen →Schweißnahtprüfung

Zerstörungsfreie Prüfung von Schweißnähten: Verfahren, Einsatzgebiete und typische Fehlerbilder bei Schweißverbindungen verständlich erklärt.

Prüfaufgabe öffnen →Grat, Kernreste & Späne

Grat, Kernreste & Späne automatisiert & schnell finden mit industrieller CT. Eine Prüfung ist bei Ihnen oder im Microvista CT-Labor möglich.

Prüfaufgabe öffnen →Weitere Branchen

Bereit für die nächste Prüfaufgabe?

Kontaktieren Sie uns für eine unverbindliche Beratung zu Ihren spezifischen Anforderungen.

GET YOUR INSPECTION DONE

Anywhere. Anytime. Fast.